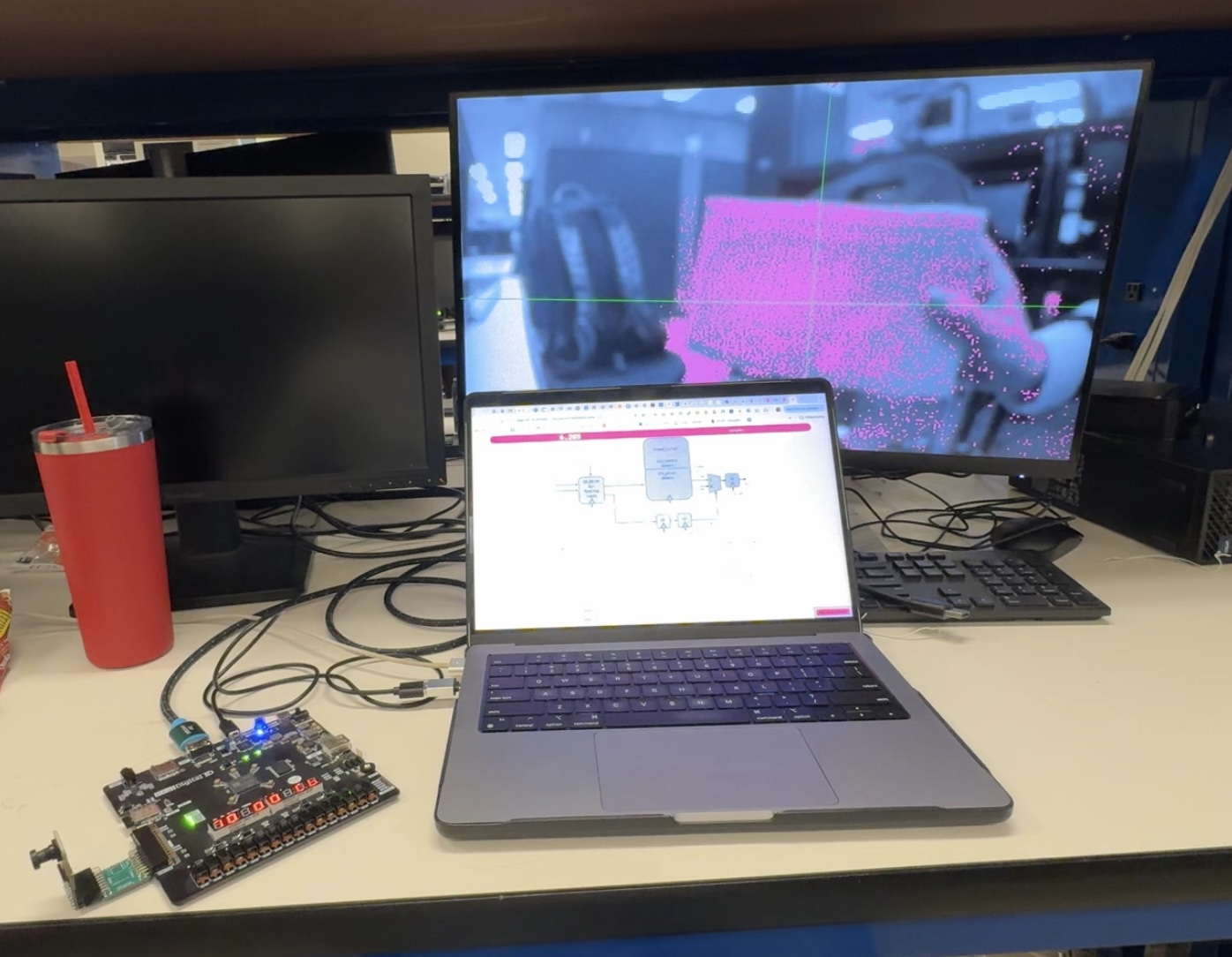

Real-Time Vision Processing System

Hardware-accelerated real-time image analysis pipeline.

Overview

A real-time vision processing pipeline implemented in hardware, capable of analyzing image streams at high frame rates with minimal latency. Hardware acceleration enables processing that would be infeasible at the required speed on a general-purpose CPU.

Architecture

Image data flows through a pipelined hardware processing chain — each stage performs a specific transformation or detection pass, with results available within a fixed number of clock cycles. The design prioritizes throughput and deterministic latency for real-time applications.